2.5 Gbits/s Optical Transponder

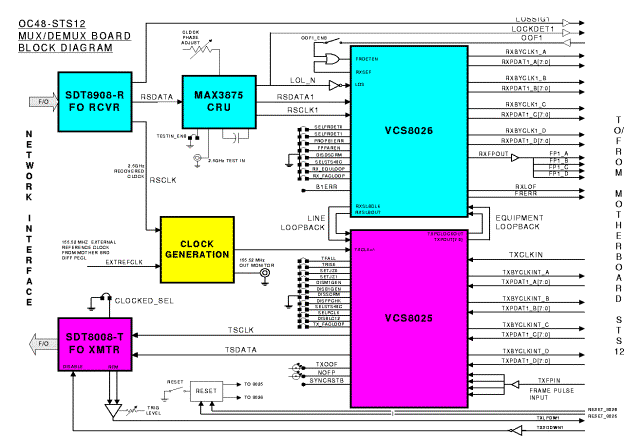

This is an old design, started before the OIF finalized an SFI interface. The unit is basically a small daughter card, designed to plug onto a line card. As seen in the block diagram below, it consists of Sumitomo optics and Vitesse MUX and DEMUX chips. The high-speed signals are routed on the top layer, which is made from Rogers RO4350 laminate. The remaining layers are plain FR4.

GENERAL DESCRIPTION

This board performs all the necessary functions for multiplexing / de-multiplexing four byte wide STS-12/STM-4 data streams into / from one OC-48 signal. The receive section accepts an OC-48 signal and generates a 2.488 Gbit/s serial data stream along with a recovered clock. The serial data is then de-multiplexed into 4 byte wide STS-12/STM-4 data streams at 77.76 MHz.

The transmit section performs the reverse operations by taking a 4 byte wide STS-12/STM-4 data stream and multiplexing it into one OC-48 signal.

GENERAL DESCRIPTION

This board performs all the necessary functions for multiplexing / de-multiplexing four byte wide STS-12/STM-4 data streams into / from one OC-48 signal. The receive section accepts an OC-48 signal and generates a 2.488 Gbit/s serial data stream along with a recovered clock. The serial data is then de-multiplexed into 4 byte wide STS-12/STM-4 data streams at 77.76 MHz.

The transmit section performs the reverse operations by taking a 4 byte wide STS-12/STM-4 data stream and multiplexing it into one OC-48 signal.

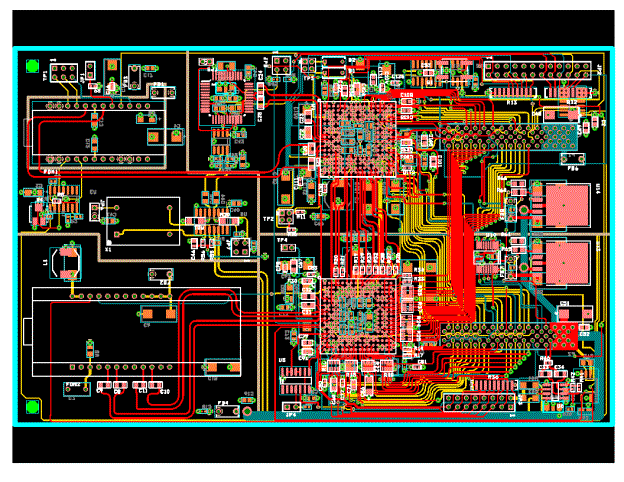

LAYOUT

six layers

six layers

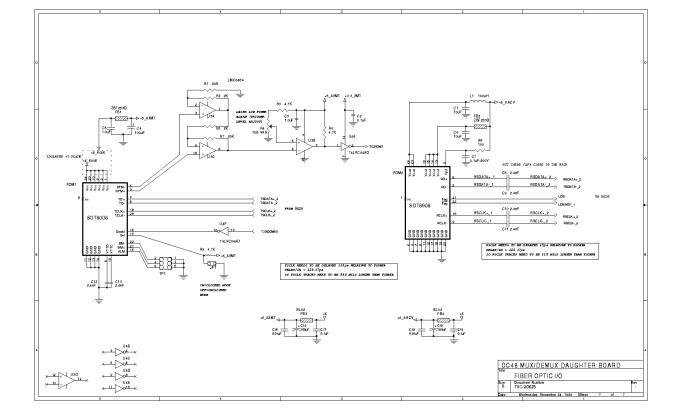

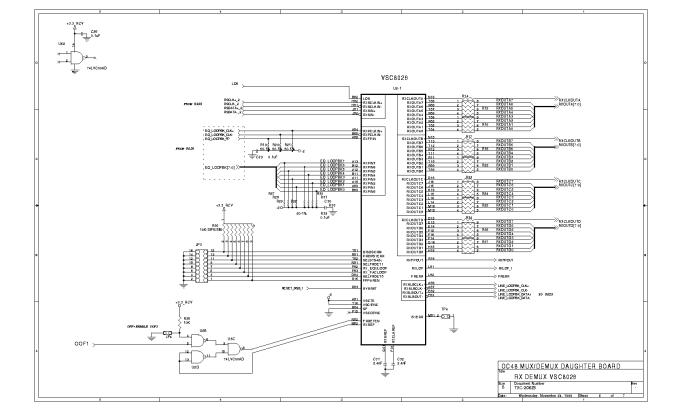

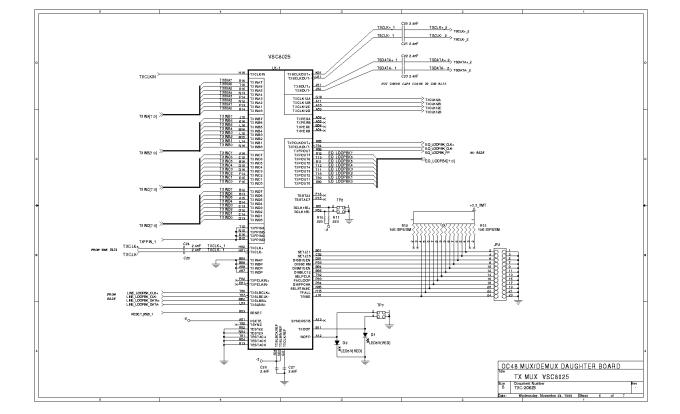

Partial schematics

Fiber optic I/O

DEMUX

MUX